Name\_\_\_\_\_ Spring 2020

Instructions: Students may bring 1 page of notes (front and back) to this exam. A scientific calculator will be provided but all personal electronic devices (smart phones, graphing calculators, ....) are not permitted. There are 10 questions and 5 problems. The points allocated to each question and each problem are as indicated. Please solve problems in the space provided on this exam and attach extra sheets only if you run out of space in solving a specific problem.

If parameters of semiconductor processes are needed beyond what is given in a specific problem or question, assume a CMOS process is available with the following key process parameters;  $\mu_n C_{OX} = 100 \mu A/V^2$ ,  $\mu_p C_{OX} = \mu_n C_{OX}/3$ ,  $V_{TNO} = 0.5V$ ,  $V_{TPO} = -0.5V$ ,  $C_{OX}=8fF/\mu^2, \lambda=0.$ If reference to a diode is made, assume the process parameter  $J_s=10^{-17}A/\mu^2$ . The ratio of Boltzmann's constant to the charge of an electron is k/q=8.61E-5 V/K. If any other process parameters for MOS devices are needed, use the process parameters associated with the process described on the attachment to this exam. Specify clearly what process parameters you are using in any solution requiring process parameters

## Short Answer Questions

EE 330

Exam 1

- (2pts) What is the approximate size of the  $SiO_2$  molecule? Give the answer in 1. angstroms ( Å ).

- 2. (2pts) One step in the photolithographic process is the "development" of the photoresist. What is the purpose of the "development" step?

- 3. (2pts) How many valence band electrons are in a silicon atom?

- 4. (2pts) What is the major difference between a diffused n-type region and an n-type epitaxial layer?

- 5. (2pts) When laying out transistors, a "dogbone" contact is often used to make contact to the gate. Why is the dogbone contact used?

- 6. (2 pts) Why is the capacitance density from Metal 2 to substrate smaller than the capacitance density from Metal 1 to substrate?

- (2pts) It took a long time for the semiconductor industry to develop practical methods for forming copper interconnects. There were two major challenges that had to be overcome. Give one of the major challenges.

- 8. (2pts) When was the understanding of pn-junctions necessary to develop the "diode equation" first reported?

- 9. (2pts) When using STI (shallow trench isolation) to form a thick SiO<sub>2</sub> layer, is thermal growth or chemical vapor deposition used to create the SiO<sub>2</sub> layer?

10. (2pts) Since the mid 1950's, the major electronic device used for amplification has been either the MOSFET or the BJT. These are both referred to as transistors and the semiconductor industry has been in the "transistor era" since the mid 1950's. What was the major electronic device that was used for amplification for the three decades preceding emergence of the transistor era?

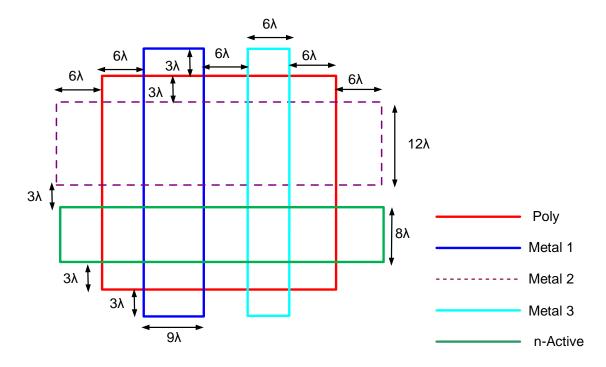

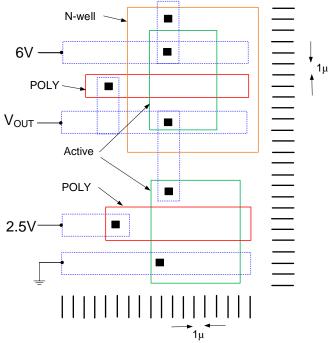

**Problem 1**(16 pts) Five non-contacting regions are shown. Assume these features are fabricated in a 0.5 $\mu$  CMOS process with  $\lambda = 0.3\mu$ .

- a) Determine the size of the transistor (i.e. W and L)

- b) Determine the parasitic capacitance from Metal 1 to Metal 3

- c) Determine the parasitic capacitance from Metal 1 to Metal 2

- d) Determine the parasitic capacitance from Metal 2 to Substrate

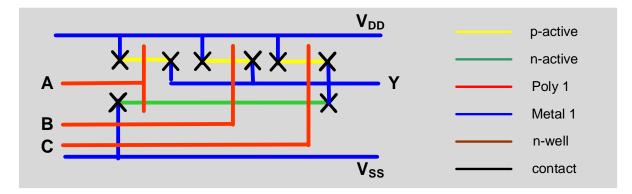

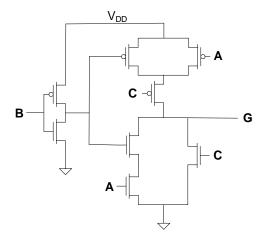

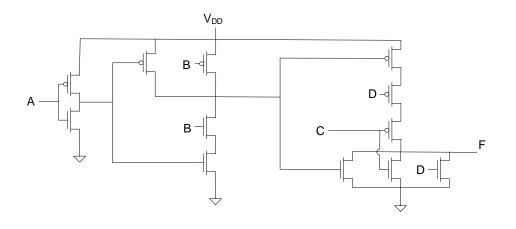

Problem 2 (16 pts) Obtain expressions for the Boolean variables Y, F, and G. Assume A, B, C, and D are Boolean inputs.

Problem 3 (16 pts) The layout of a simple circuit is shown below. Obtain the circuit schematic including device dimensions for all devices.

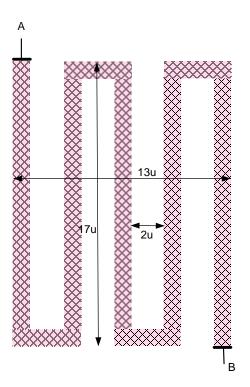

**Problem 4** (16 pts) An n+ diffused resistor designed in a 0.5 $\mu$  process is shown below where the individual traces in the resistor are all 1 $\mu$ m wide and where the two ends of the resistor are labeled as A and B in the figure. Assume the sheet resistance for the 0.5 $\mu$ process is as given in the attached table where the given values are for operation at T=250K. Assume further that the TCR of the n+ diffused resistors are constant of value 1200 ppm/°C.

- a) Determine the resistance between nodes A and B at T=250K.

- b) What will be the resistance at  $T=300^{\circ}K$ ?

Problem 5 (16 pts)Assume the cost of 12" wafers in a CMOS process is \$1200and the defect density is  $1.2/cm^2$ . If the cost per good die on a project must not exceed \$1.50,what is the maximum area that can be used for the die?Assume a 100% soft yield.

## MOSIS WAFER ACCEPTANCE TESTS

| RUN: T6AU         |              | VENDOR: AMIS        |

|-------------------|--------------|---------------------|

| TECHNOLOGY: SCN05 |              | FEATURE SIZE: 0.5µm |

|                   | Dun time CVD |                     |

Run type: SKD

INTRODUCTION: This report contains the lot average results obtained by MOSIS from measurements of MOSIS test structures on each wafer of this fabrication lot.

| TRANSISTOR PARAMETERS                  | W/L      | N-CHANNEI                     | UNITS                           |                               |

|----------------------------------------|----------|-------------------------------|---------------------------------|-------------------------------|

| MINIMUM<br>Vth                         | 3.0/0.6  | 0.79                          | -0.92                           | volts                         |

| SHORT<br>Idss<br>Vth<br>Vpt            | 20.0/0.6 | 446<br>0.68<br>10.0           | -239<br>-0.90<br>-10.0          | uA/um<br>volts<br>volts       |

| WIDE<br>Ids0                           | 20.0/0.6 | < 2.5                         | < 2.5                           | pA/um                         |

| LARGE<br>Vth<br>Vjbkd<br>Ijlk<br>Gamma | 50/50    | 0.68<br>10.9<br><50.0<br>0.48 | -0.95<br>-11.6<br><50.0<br>0.58 | volts<br>volts<br>pA<br>V^0.5 |

| K' (Uo*Cox/2)<br>Low-field Mobility    |          | 56.4<br>463.87                | -18.2<br>149.69                 | uA/V^2<br>cm^2/V*s            |

COMMENTS: Poly bias varies with design technology. To account for mask bias use the appropriate value for the parameter XL in your SPICE model card.

| (um)                                                                                          | Design Technology                               | XL (um) XW                                               |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------------|

| ( )                                                                                           | SCMOS_SUBM (lambda=0.30)<br>SCMOS (lambda=0.35) | 0.10 0.00<br>0.00 0.20                                   |

| FOX TRANSISTORS<br>Vth                                                                        | GATE N+ACTIVE P+ACTIVE<br>Poly >15.0 <-15.0     | UNITS<br>volts                                           |

| PROCESS PARAMETERS N+<br>Sheet Resistance 83<br>Contact Resistance 64<br>Gate Oxide Thickness | 8.5 105.3 23.5 999 44.2 0   4.9 149.7 17.3 29.2 | M1 M2 UNITS<br>.09 0.10 ohms/sq<br>0.97 ohms<br>angstrom |

| PROCESS PARAMETERS<br>Sheet Resistance<br>Contact Resistance                                  | M3 N\PLY N_W<br>0.05 824 816<br>0.79            | UNITS<br>ohms/sq<br>ohms                                 |

COMMENTS: N\POLY is N-well under polysilicon.

| CAPACITANCE PARAMETERS<br>Area (substrate)<br>Area (N+active)<br>Area (P+active) | N+<br>425 | ₽+<br><b>731</b> | POLY<br>84<br>2434<br>2335 | POLY2 | M1<br>27<br>35 | M2<br>12<br>16 | M3<br>7<br>11 | N_W<br>37 | UNITS<br>aF/um^2<br>aF/um^2<br>aF/um^2 |

|----------------------------------------------------------------------------------|-----------|------------------|----------------------------|-------|----------------|----------------|---------------|-----------|----------------------------------------|

| Area (poly)                                                                      |           |                  |                            | 938   | 56             | 15             | 9             |           | aF/um^2                                |

| Area (poly2)                                                                     |           |                  |                            |       | 49             |                |               |           | aF/um^2                                |

| Area (metall)                                                                    |           |                  |                            |       |                | 31             | 13            |           | aF/um^2                                |

| Area (metal2)                                                                    |           |                  |                            |       |                |                | 35            |           | aF/um^2                                |

| Fringe (substrate)                                                               | 344       | 238              |                            |       | 49             | 33             | 23            |           | aF/um                                  |

| Fringe (poly)                                                                    |           |                  |                            |       | 59             | 38             | 28            |           | aF/um                                  |

| Fringe (metal1)                                                                  |           |                  |                            |       |                | 51             | 34            |           | aF/um                                  |

| Fringe (metal2)                                                                  |           |                  |                            |       |                |                | 52            |           | aF/um                                  |

| Overlap (N+active)                                                               |           |                  | 232                        |       |                |                |               |           | aF/um                                  |

| Overlap (P+active)                                                               |           |                  | 312                        |       |                |                |               |           | aF/um                                  |

| CIRCUIT PARAMETERS      |     |        | UNITS       |

|-------------------------|-----|--------|-------------|

| Inverters               | K   |        |             |

| Vinv                    | 1.0 | 2.02   | volts       |

| Vinv                    | 1.5 | 2.28   | volts       |

| Vol (100 uA)            | 2.0 | 0.13   | volts       |

| Voh (100 uA)            | 2.0 | 4.85   | volts       |

| Vinv                    | 2.0 | 2.46   | volts       |

| Gain                    | 2.0 | -19.72 |             |

| Ring Oscillator Freq.   |     |        |             |

| DIV256 (31-stg,5.0V)    |     | 95.31  | MHz         |

| D256_WIDE (31-stg,5.0V) |     | 147.94 | MHz         |

| Ring Oscillator Power   |     |        |             |

| DIV256 (31-stg,5.0V)    |     | 0.49   | uW/MHz/gate |

| D256_WIDE (31-stg,5.0V) |     | 1.01   | uW/MHz/gate |